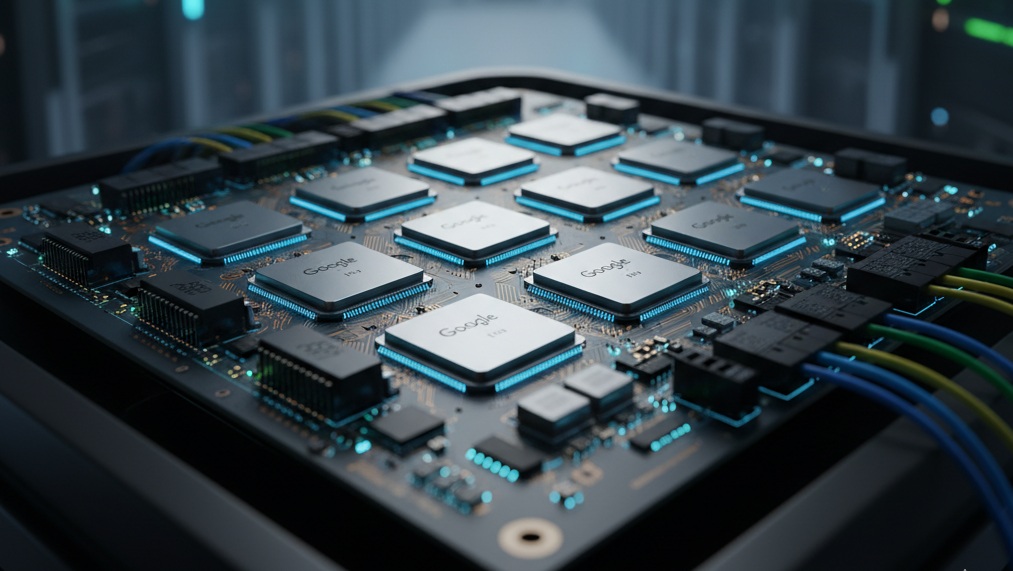

Una Unidad de Procesamiento Tensorial, o TPU por sus siglas en inglés (Tensor Processing Unit), es un tipo de Circuito Integrado de Aplicación Específica (ASIC) desarrollado por Google.

Su creación responde a la necesidad de acelerar las inmensas cargas de trabajo computacional inherentes al campo del aprendizaje automático y, específicamente, al aprendizaje profundo. Mientras las CPU y GPU fueron diseñadas para propósitos más amplios, el TPU es una pieza de hardware construida desde cero con un enfoque singular en las operaciones de IA.

El diseño del TPU está intrínsecamente ligado al concepto matemático del tensor, que es la estructura de datos clave utilizada en los modelos de Deep Learning. Un tensor es esencialmente una matriz de múltiples dimensiones. La operación fundamental en el entrenamiento y la ejecución de una red neuronal es la multiplicación y acumulación de matrices, que se resume en la fórmula W⋅X+b.

El corazón de la arquitectura: la matriz sistólica

La innovación tecnológica más significativa del TPU reside en su arquitectura de Matriz Sistólica. Este es un sistema donde miles de unidades de multiplicación y acumulación (MXU) están conectadas directamente entre sí. Esta interconexión física permite que los datos fluyan a través de la matriz en un proceso continuo y coordinado.

La ventaja principal de este diseño es que elimina el «cuello de botella de von Neumann» que afecta a las arquitecturas tradicionales. Al procesar los datos directamente mientras fluyen entre las unidades, el TPU reduce la necesidad de acceder repetidamente a la memoria externa, que es un proceso mucho más lento en comparación con la velocidad de cálculo dentro del chip.

Tecnológicamente, este enfoque se traduce en una capacidad para alcanzar un alto rendimiento computacional con una eficiencia energética superior. Al especializarse en las operaciones de tensores, el hardware no tiene que dedicar recursos ni tiempo a la flexibilidad que requieren los procesadores de uso general.

Además, los TPU operan de manera eficiente utilizando precisiones numéricas bajas (como 8 o 16 bits) para sus cálculos de matrices. Aunque esto implica una ligera pérdida de precisión en comparación con la coma flotante de alta precisión, resulta ser más que suficiente para la mayoría de los algoritmos de redes neuronales, a la vez que reduce drásticamente el consumo de energía y acelera aún más el procesamiento.

Desde su lanzamiento en 2016, Google ha seguido mejorando las TPU a través de múltiples generaciones, aumentando exponencialmente su rendimiento y capacidad. Las versiones más recientes no solo se utilizan para la etapa de inferencia (la ejecución de modelos entrenados), sino también para el entrenamiento (la etapa en que el modelo aprende a partir de grandes volúmenes de datos).

Su uso es crucial para impulsar los principales servicios de inteligencia artificial de Google a escala, incluyendo aplicaciones de reconocimiento de imágenes, traducción en tiempo real y el desarrollo de grandes modelos de lenguaje. El TPU representa un cambio de paradigma hacia el hardware específico de dominio como la clave para desbloquear la próxima generación de la Inteligencia Artificial.